Opal Module Components

Martin Welford

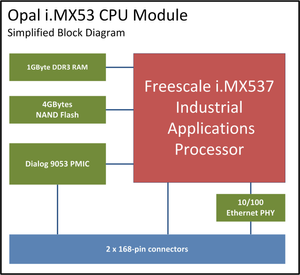

This section provides an overview of the Opal CPU Module and its capabilities. Click on the block diagram for a larger image.

Freescale i.MX53 Applications Processor

The Freescale i.MX53 applications processor is central component of the Opal CPU Module. It incorporates a Cortex-A8 core running at 800MHz (optionally up to 1.2GHz), along with memory controllers and peripherals which enable connections to a wide range of devices.

Read the i.MX53 Features chapter for more details.

Memory

The Opal CPU Module includes:

- 512Mbytes or 1Gbyte DDR3 memory.

- 512Mbytes - 2Gbytes NAND Flash (optional)

If NAND flash is not fitted, Opal can boot from an SD Card on the base-board.

10/100 Ethernet

The i.MX53 includes a 10/100 Ethernet MAC, and the Opal module expands on this functionality by adding a Micrel KSZ8051 PHY. For detailed information on the MAC, refer to the Freescale documentation.

The signals present on the Opal interface are:

Pad | Voltage | Signal Name | Description |

|---|---|---|---|

A-83 | Analog | ETHERNET_TX+ | Ethernet Transmit+ signal |

A-82 | Analog | ETHERNET_TX- | Ethernet Transmit- signal |

A-78 | Analog | ETHERNET_RX- | Ethernet Receive- signal |

A-79 | Analog | ETHERNET_RX+ | Ethernet Receive+ signal |

A-80 | 3.3V | ETHERNET_LED0 | PHY LED 0 signal |

A-81 | 3.3V | ETHERNET_LED1 | PHY LED 1 signal |

Power Management

Opal includes a Dialog Semiconductor DA9053 Power Management IC. This provides power supplies for the i.MX53 and a number of extra features including battery management, touch-screen and analog inputs. This page has more details on the capabilities of this part.

Debug

Programming and debugging software on the Opal CPU module can be done in a number of ways depending on tools available. These include:

- JTAG. Standard JTAG signals available are TMS, TCK, TDI, TDO and TRST. This requires a JTAG debugger or programmer and appropriate software.

- USB and serial boot mode.

- Ethernet